Functional Implementation of the 6502 Microprocessor in LabVIEW

This post marks a significant milestone in my personal project: the development of a complete Commodore 64 (C64) emulator entirely in LabVIEW. After successfully implementing the SID audio chip, the focus shifted to the core component: the CPU, the MOS Technology 6502 (or its 6510 variant).

I have completed the functional implementation of the 6502 core. The primary goals were achieving maximum logical accuracy while ensuring efficient execution through a lean and optimized LabVIEW codebase.

The MOS Technology 6502: History and Architecture

The 6502 is an 8-bit microprocessor that redefined the computing landscape starting in 1975. Developed by a team of former Motorola engineers led by Chuck Peddle, it was launched at a groundbreaking price of just \$25, making it accessible to home computer manufacturers and undercutting competitors like the Intel 8080 or Motorola 6800. It served as the engine for legendary machines such as the Apple II, Atari 2600, Nintendo Entertainment System (NES), and, of course, the Commodore 64.

Technical Details

Despite its low cost, the 6502 was ingeniously designed for efficiency. Unlike CPUs with extensive register sets, the 6502 operates with only three main 8-bit registers, relying heavily on memory (RAM) for temporary data storage, particularly the Zero Page (the first 256 bytes), which can be accessed much faster.

The architecture relies on:

- - 8-bit Registers:

- - System Registers:

Its advanced addressing modes (like Indirect Indexed and Indexed Indirect) are key to its speed and have been meticulously replicated in the LabVIEW code.

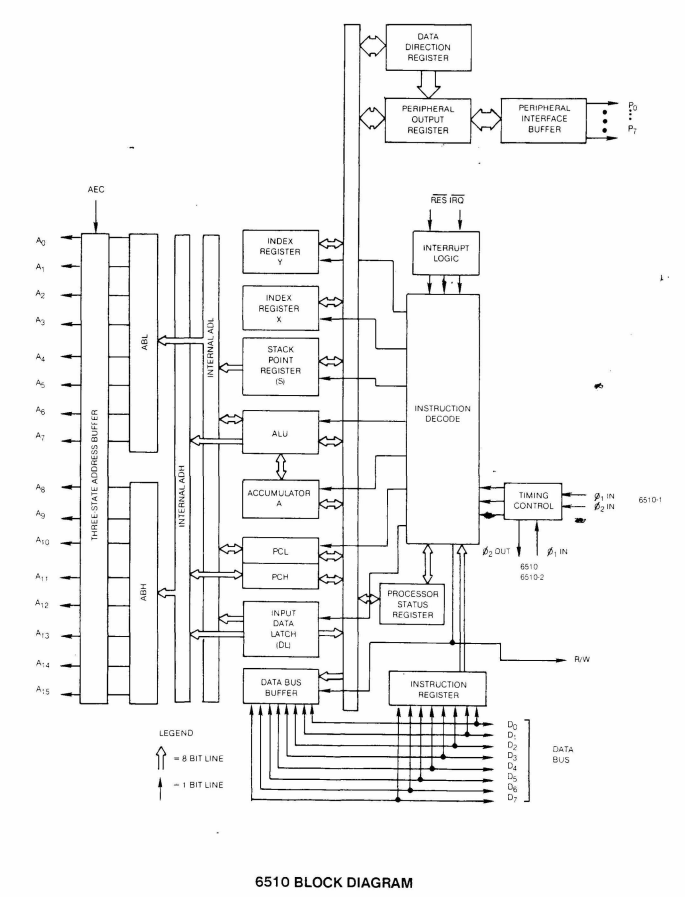

Below the block diagram of 6510 CPU, source http://archive.6502.org/datasheets/mos_6510_mpu.pdf

The LabVIEW Implementation: Lean and Fast

The chosen approach for the LabVIEW implementation prioritized direct logic and the absence of complex abstractions.

Code Efficiency

The choice to use only basic LabVIEW functions and to avoid sophisticated design structures (like the Actor Framework or Object-Oriented code) was not merely for clarity; it was a performance necessity. LabVIEW, not being a native language for emulation, demands that the code be as "lean" as possible to minimize execution overhead. The logical mapping of the *fetch-decode-execute* cycle was implemented within a main loop using a Case Structure with 256 branches, ensuring that each instruction is handled with the fewest possible intermediate operations, thereby optimizing execution speed.

Functional Replication

The implementation is purely functional. My primary focus was on replicating the logical correctness of every instruction's outcome and the precise manipulation of registers and simulated memory (a LabVIEW array). Hardware bus modeling or cycle-accurate logic at the transistor level was not implemented, as the goal was full software compatibility. The code implements all 151 documented instructions of the NMOS 6502, including sensitive operations like handling the Decimal Mode (BCD).

This broad coverage is fundamental to ensuring the emulator can execute the vast C64 software library. My implementation focuses on the precise functional replication of these instructions.

The implemented opcodes can be grouped into the following functional categories:

| Logical Function | Mnemonics |

|---|---|

| Flow Control | BRK, JSR, RTI, JMP, RTS |

| Conditional Branches | BPL, BMI, BVC, BVS, BCC, BCS, BNE, BEQ |

| Logic Operations | ORA, AND, EOR |

| Shift / Rotate | ASL, ROL, LSR, ROR |

| Flag Control | CLC, SEC, CLI, SEI, CLV, CLD, SED |

| Stack Operations | PHP, PLP, PHA, PLA |

| Load / Store | LDA, STA, LDX, STX, LDY, STY |

| Register Transfer | TXA, TYA, TXS, TAY, TAX, TSX |

| Increment / Decrement | DEC, INC, INY, DEX, INX, DEY |

| Compare | CPY, CPX, CMP |

| Arithmetic | ADC, SBC |

| BIT Test | BIT |

| No Operation | NOP |

The Definitive Test: The Klaus Dormann Test Suite

The validity of a 6502 emulator is measured by its ability to pass the Klaus Dormann Test Suite. This is not a simple functional test; it is an extremely critical and comprehensive benchmark that probes the *micro-logics* and *edge cases* of the processor.

The Complexity of the Test

Passing this suite is challenging because it requires the emulator to perfectly handle every subtle aspect, including:

- - Flag Setting: It verifies that all 7 Status Flags (P) are set correctly after every operation, including tricky conditions like the Overflow (V) flag and correct Carry (C) propagation cases.

- - Decimal Mode (BCD): It rigorously tests the arithmetic in Decimal Mode, an operation that involves unique Carry and Zero rules and is frequently a point of failure for emulators.

- - Opcode/Addressing Mode Combinations: It tests the execution of every instruction in all its supported addressing modes, ensuring no specific *bugs* exist in less frequent combinations.

The LabVIEW implementation fully passes the Klaus Dormann Test Suite. This result certifies the functional accuracy of the LabVIEW code, achieving an execution performance of approximately 4 MHz (emulated clock cycles per second) on a mid-range machine—a speed more than adequate for emulating 1 MHz systems like the C64.

Project Outlook

With the 6502 CPU now validated and performant, the project moves forward on a solid foundation. The next critical components to implement are the CIA1 (Complex Interface Adapter) for interrupt and keyboard input management, and the memory management architecture (including the PLA logic).

The Code

The code for the 6502 implementation, including the LabVIEW program used to execute the rigorous Klaus Dormann test, is available on GitHub:

https://github.com/ale914/C64_labview_emu

Klaus Dormann Test Program Location: The program that executes the test is located in the folder bin\CPU\test\ within the repository.